Les processeurs informatiques

Publié le 16/09/2012

Extrait du document

Le processeur est un circuit logique synchrone. Un circuit logique est un circuit électronique dont les composantes peuvent prendre l'un des 2 états, désignés par 0 ou 1, suivant la tension à leurs bornes. Il est dit synchrone quand tous les composants attendent le prochain signal d'horloge pour passer à l'état suivant. L'horloge est intégrée dans le processeur et fonctionne à une fréquence fixe pendant toute la durée de vie du processeur. Elle osci lle entre les 2 états, 0 et 1, de façon périodique et continue.

«

nombre formé par 8 bits est un octet (byte en anglais).

Les anciens processeurs traitaient les nombres par tranches de 4 bits.

Aujourd'hui , les processeurs les plus récents traitent des ensembles de 64 bits à la fois.

ARCHITECTURE SIMPLIFIÉE ET FONCTION S

É LÉMENTAIRES Le processeur est un circuit logique synchrone.

Un circuit logique est un circui t électronique dont les composantes peuvent prendre l'un des 2 états, désignés par 0 ou 1 , suivant la tensio n à leurs bornes.

Il est dit synchrone quand tous les composants attendent le prochain signal d'horloge pour passer à l'état suivant.

L'horloge est intégrée dans le p rocesseur et fonctionne à une fréquence fixe pendant toute la durée de vie du processeur.

Elle osci lle entre les 2 états, o et 1, de façon périodique et continue .

Bus Un bus, en informatique, est un ensemble de liaisons physiques (câb les, pistes de circuits imprimés , etc.)

pouvant être exploitées en commun par plusieurs é léments matérie ls afin de communiquer entre eux.

L'unité arithmétique et logique (UAL ) C'est l'organe de base d u processeur.

Il est chargé des calculs et des opérations qu'on peut réparti r comme suit: • Les opéra tions arithmé tiques simples telles que addition, soustraction et changement de signe.

• Les opérations logiques telles q ue NON (inversion des b its), ET (intersection) et OU (union).

• Les comparaisons telles que les tests d'éga lité, de s upério rité ou d 'i nfériorité.

• Éventuellement des déca lages ou des rotations.

Les opérations plus complexes sont

traitées au niveau logiciel par les compilate urs.

Ains i une multiplication est une suite de p lusieurs additions.

Toutefois, dans les nouveaux processeurs, les UAL peuvent effectuer des opérations plus comp lexes, comme des racines , des logarithme s, ou l'inverse d 'un nombre .

Typiquement , sous la forme la plus simple, I'UAL possède une entrée par laquelle elle reçoit l'ordre à exécuter, une ou plusieu r s entrées où a rrivent les variables à traiter , et une sortie où est récupéré le résu ltat.

Registres Un registre est une case mémoire, à utilisation tempora ire, intégrée dans le circuit du processeur.

Il a pour fonction de s tocker des variab les utiles au fonctionnement du processeur et à l'exécution rapide du programme .

Les registres peuvent être à usage général (stockage d'un résultat) ou bien à usage spécifique .

Ainsi il existe un nombre de registres spécialisé s nécessaires au fonctionnement du processeur : registres de flags, adresse du segment de code, adresse du segment de données ...

Mémoire cache Le processeur d 'un ordinateur utilise la mémo ire vive (RAM) pour les calculs, et les traitements .

Toute fois, dans certains cas, il a besoin de stocker des variables de petite taille et d'y accéde r répétitivement et rapidement.

La mémoi re cache est une mémoire relativement petite , très rapide d'accès, de plus grande capacité que les registres, intégrée d irectement sur le processeur .

Elle sert à accélérer les traitements.

Adressage -Compteur ordinal ou pointeur d 'instrud i on Le processe ur doit accéder d 'une part au code du programme à exécuter et d'autre part aux variables à traiter.

Tout étant chargé en mémo ire, il existe un système d'adressage permettant au processeu r de bien récupérer toutes les données .

La mémoire est ainsi divisée en p lu s ieurs parties appelées segments.

Le code est chargé dans un segment et les données dans un autre segment.

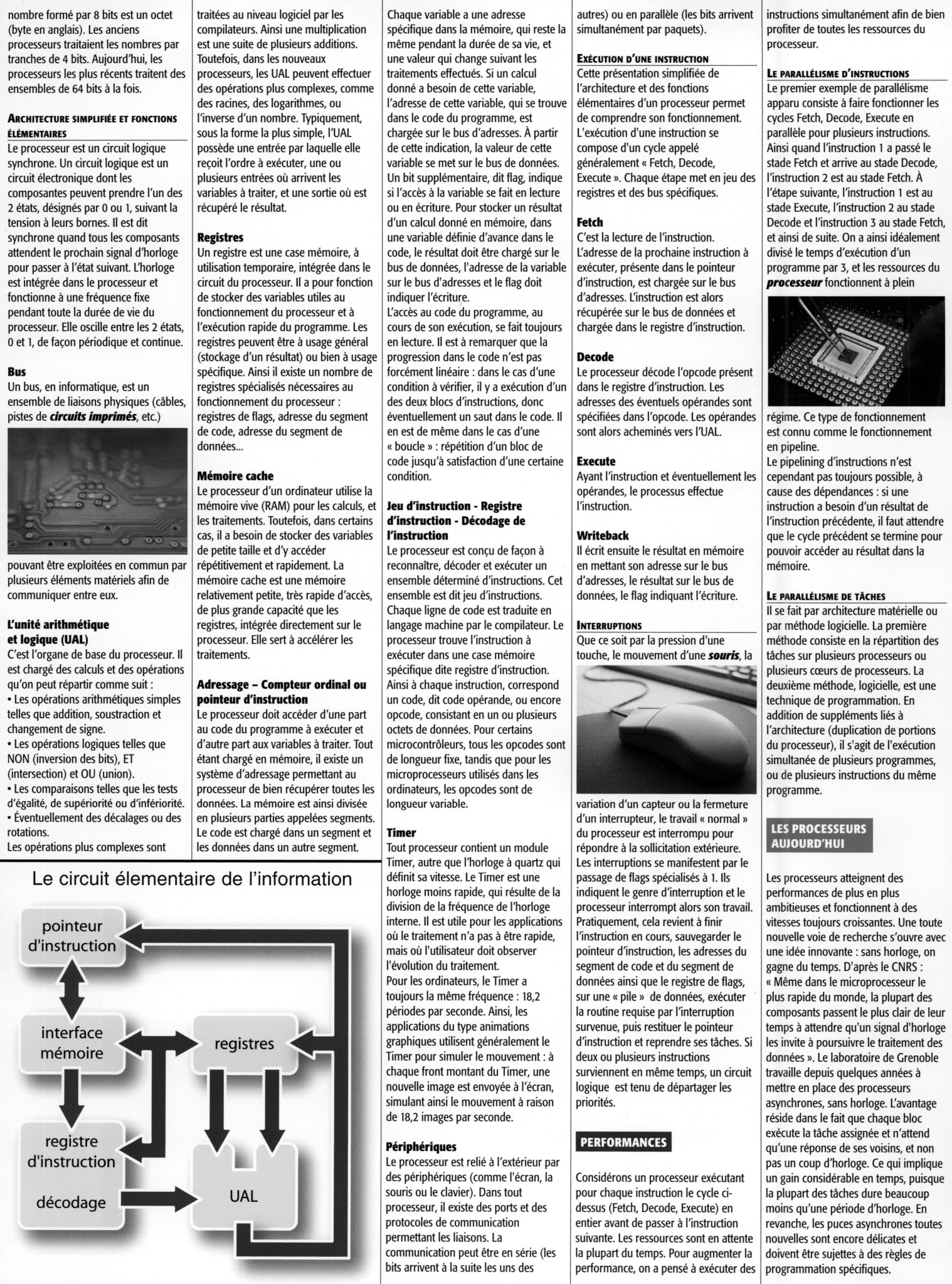

Le circuit élemen t aire de l'information

registre

d 'instruction

décodage

registres

Chaque variable a une adresse spécifique dans la mémoire, qui reste la même pendant la durée de sa vie, et une valeur qui change suiva nt les traitements effectués.

Si un calcul donné a besoin de cette variable, l'adresse de cette variable, qui se trouve dans le code du programme, est chargée sur le bus d'adresses.

À partir de cette indication , la valeur de cette variab le se met sur le bus de données .

Un bit supp lémentaire, dit flag, indique si l'accès à la variable se fait en lecture ou en écriture.

Pour stocke r un résu ltat d 'un calcul donné en mémoire, dans une variable définie d'avance dans le code, le résultat doit être chargé sur le bus de donnée s, l'adresse de la variable sur le bus d 'adresses et le flag doit indiquer l'écriture.

L'accès au code du programme , au cours de son exécution, se fait toujours en lecture .

Il est à remarquer q ue la progression dans le code n'est pas forcément linéa ire: dans le cas d'une condition à vérifier, il y a exécution d 'un des deux blocs d'instructions, donc éventue llement un saut dans le code.

Il en est de même dans le cas d'une « boucle » : répétition d'un bloc de code jusqu'à satisfaction d'une certaine condition.

Jeu d'instrudion - Registre d'instrudion - Décodage de l'instrudion Le processeur est conçu de façon à reconnaître , décoder et exécuter un ensemble déterminé d'instructions.

Cet ensemble est dit jeu d'instructions .

Chaque ligne de code est traduite en langage machine par le compilateur.

Le processeur trouve l'instruction à exécuter dans une case mémoire spéci fique dite registre d'instruction.

Ainsi à chaque instruction, correspond un code, d it code opérande, ou encore opcode, consistant en un ou p lusieurs octets de donnée s.

Pour certains microcontrôleurs, tous les opcodes sont de longueur fixe, tandis que pour les microp rocesseurs utilisés dans les ordinateu rs, les opcodes sont de longueur variable.

Ti mer Tout processeur contient un module limer , autre que l'horloge à quartz qui définit sa vitesse.

Le Timer est une horloge moin s rapide , qui résulte de la division de la fréquence de l'horloge interne .

Il est utile pour les app lications où le traitement n'a pas à être rapide , mais où l'u til isateur doit observer l'évo lution du traitement.

Pour les ordinateurs, le Timer a toujour s la même fréquence : 18,2 périodes par seconde .

Ainsi , les applications du type animations graphiques utilisent généralement le T imer pour simuler le mouvement : à chaq u e front montant du Timer , une nouvelle image est envoyée à l'écran, simulant ainsi le mouvement à raison de 18,2 images par seco nde.

Périphériques Le proc esseur est relié à l'exté rieur par des périphérique s (comme l'écran, la sour is ou le clavier) .

Dans tout processeur , il existe des ports et des protocoles de communication permettant les liaison s.

La communication peut être en série (les bits arrivent à la suite les uns des

autres) ou en para llè le (les bits arrivent instructions simultanément afin de bien simultanément par paquets) .

profiter de toute s les ressources du processe ur.

EXÉCUTION D 'UNE INSTRUCTION Cette présentation simplifiée de LE PARALLÉLISME D'INmUCTIONS l'architecture et des fonctions L e premier exemple de parallélisme é lémentaires d'un proce sseur permet appar u consiste à faire fonctionner les de comprendre son fonctionnement.

cycles Fetch , Decode, Execute en L'exécution d'une instruction se parallèle pour p lusieurs instructions.

compose d'un cycle appelé Ainsi quand l'instruction 1 a passé le généralement « Fetch, Decode , stade Fetch et arrive au stade Decode, Execute ».

Chaque étape met en jeu des l'instruction 2 est au stade Fetch .

À registre s et des bus spécifique s.

l'étape suivante, l'instruction 1 est au stade Execute, l'instruction 2 au stade Fetch Decode et l'instruction 3 au stade Fetch , C'est la lecture de l'instruction .

et ainsi de suite.

On a ainsi idéalement L'adre sse de la prochaine instruction à divisé le temps d'exécution d 'u n exécuter, présente dans le pointeur programme par 3, et les ressou rces du d'inst ruction , est chargée sur le bus pro cesseur fonctio nnent à p lein d'adre sses .

L'instruction est alors récupérée sur le bus de données et chargée dans le registre d'instr uction .

Decode Le processeur décode l'opcode présent dans le registre d 'instruct ion.

Les adresses des éventuels opérandes sont spécifiées dans l'opcode.

Les opérandes régime.

Ce type de fonctionnement sont alors acheminés vers I'UAL.

est connu comme le fonctionnement en pipe line.

Execute Le pipe lining d 'instr uctions n'est Ayant l'instruction et éventuellement les cependant pas toujours possible , à opérandes, le processus effectue cause des dépendances : si une l'instruction.

instruction a besoin d 'un résu ltat de l'instruction précédente , il faut attendre Writeback que le cycle précédent se termine pour Il écrit ensuite le résultat en mémoire pouvoir accéder au résultat dans la en mettant son adresse sur le bus mémoire.

d'adresse s, le résu ltat sur le bus de données , le flag indiquant l'écriture .

LE PAR A LL ÉLISME DE T ACHES Il se fait par architectu re matérielle ou INTERRUPTIONS par méthode logicielle .

La p remière Que ce soit par la pression d'une méthode consiste en la répartition des touche, le mouvement d 'une souris , la tâches sur plusieurs processeur s ou plusieurs cœurs de processeurs .

La deuxième méthode , logicie lle, est une technique de programmat ion.

En ~ addition de suppléments liés à ët l'architecture (duplication de portions "'> de données , exéc uter plus rapide du monde, la plupart des w,-w '9' la routine requise par l'interruption composants passent le plus clair de leur "''"""-::5o" N.!l survenue, puis restituer le pointeur temps à attendre qu'un s ignal d 'horloge !.

»

↓↓↓ APERÇU DU DOCUMENT ↓↓↓

Liens utiles

- TPE SUR LES PROCESSEURS INFORMATIQUES

- réseaux informatiques.

- Les systèmes informatiques et leur sécurité

- réseaux informatiques - informatique.

- «Titre», Ma surprise fut énorme à la réception de la facture n°5468 correspondant à l'achat de quelques accessoires informatiques : elle s'élève en effet à 15 500 FF !